Home

Welcome on the Math2mat website.

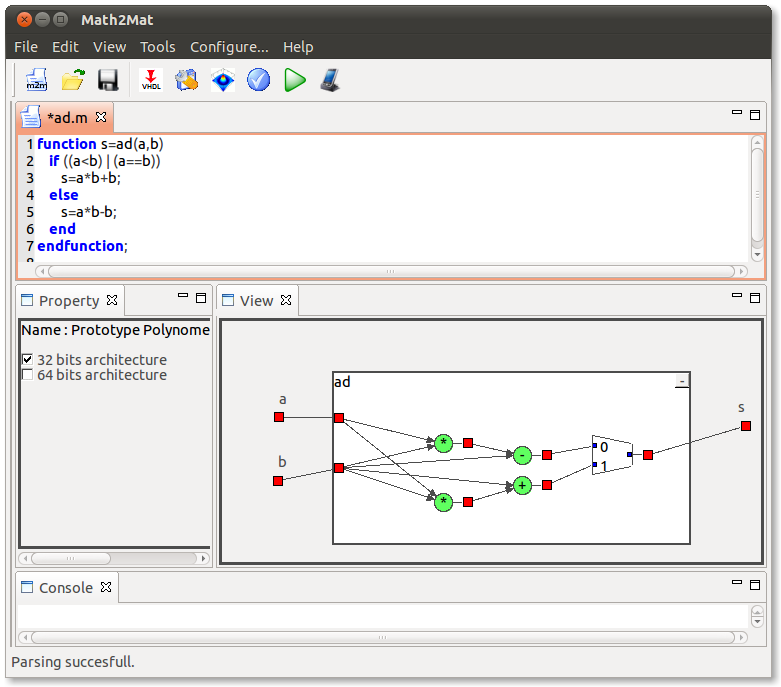

The aim of the Math2mat software is to automatically generate a VHDL description of a mathematical function using floating point operators. It also generates a full SystemVerilog testbench that allows to validate the hardware description by comparing it to the initial mathematical description. The initial description corresponds to the Octave syntax (compatible with Matlab), and allows operations such as addition, subtraction, multiplication, division, and structures such as if/then/else and for loops.

The main features of Math2mat are:

• Editor for typing Octave code

• Dynamic code analysis, during typing

• Generation of synthesizable VHDL code

• Floating point operations

• SystemVerilog testbench generation

• Fully automated test suite for the generated code

• Graphical interface with internal structure viewing

Math2mat provides a graphical interface as show in the figure below. Command line

operations using a subset of the Java classes are also possible, and are documented in

the developer guide.

Math2Mat

Math2Mat